NVMe (non-volatile memory express) est une interface de contrôleur hôte et un protocole de stockage créés pour accélérer la vitesse de transfert des données entre les systèmes d’entreprise et les systèmes clients et les disques SSD via le bus PCIe (High-speed Peripheral Component Interconnect Express) d’un ordinateur.

Comme la technologie à semi-conducteurs est devenue le support privilégié sur le marché du stockage, il est rapidement devenu évident que les interfaces et les protocoles existants – notamment les connexions SATA (Serial Advanced Technology Attachment) et SAS (Serial-Attached SCSI) – ne convenaient pas, en particulier dans les environnements de centre de données. Les travaux sur un nouveau protocole conçu spécifiquement pour le flash NAND ont commencé dès 2007, Intel prenant les devants. Au début de 2011, la spécification NVMe initiale a été publiée – près de 100 entreprises technologiques ont été impliquées dans le développement.

La spécification NVMe définit une interface de registre, un ensemble de commandes et une collection de fonctionnalités pour les SSD basés sur PCIe avec les objectifs de hautes performances et d’interopérabilité sur un large éventail de sous-systèmes NVM. La spécification NVMe ne spécifie pas le modèle d’utilisation ultime, tel que le stockage à semi-conducteurs, la mémoire principale, la mémoire cache ou la mémoire de sauvegarde.

NVMe fournit une alternative à la norme SCSI (Small Computer System Interface) et à la norme ATA pour la connexion et la transmission de données entre un système hôte et un périphérique de stockage cible. Le jeu de commandes ATA utilisé avec les SSD SATA et le jeu de commandes SCSI pour les SSD SAS ont été développés à une époque où les disques durs (disques durs) et les bandes étaient les principaux supports de stockage. NVMe a été conçu pour être utilisé avec des supports plus rapides.

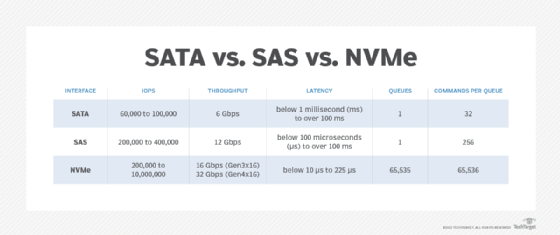

Les principaux avantages des SSD PCIe basés sur NVMe par rapport aux SSD basés sur SAS et SATA sont une latence réduite dans la pile logicielle hôte, des opérations d’entrée / sortie par seconde (IOPS) plus élevées et une consommation d’énergie potentiellement plus faible, en fonction du facteur de forme et du nombre de voies PCIe utilisées.

Le protocole NVMe peut prendre en charge les SSD qui utilisent différents types de mémoire non volatile, y compris le flash NAND et la technologie 3D XPoint développée par Intel et Micron Technology. Les pilotes de référence NVMe sont disponibles pour une variété de systèmes d’exploitation (OS), y compris Windows et Linux.

NVMe ne permet pas seulement aux applications existantes de s’exécuter plus rapidement et plus efficacement; c’est en fait un facilitateur clé des technologies et applications nouvelles et en évolution telles que l’Internet des objets (IoT), l’intelligence artificielle (IA) et l’apprentissage automatique (ML), qui peuvent toutes bénéficier de la faible latence et des hautes performances du stockage connecté NVMe.

Fonctionnement de NVMe

NVMe mappe les commandes d’entrée/sortie (E/S) et les réponses à la mémoire partagée d’un ordinateur hôte via l’interface PCIe. L’interface NVMe prend en charge les E / S parallèles avec des processeurs multicœurs pour faciliter le débit élevé et atténuer les goulots d’étranglement des unités de traitement centrales (CPU).

NVMe offre un ensemble de commandes plus simplifié pour traiter une requête d’E / S que les ensembles de commandes SCSI et ATA. NVMe nécessite moins de la moitié du nombre d’instructions CPU que le jeu de commandes SCSI avec les périphériques SAS et que le jeu de commandes ATA utilise avec les disques SATA.

SSD NVMe par rapport aux SSD SATA

SATA est un protocole de communication développé pour que les ordinateurs interagissent avec les systèmes de stockage sur disque dur. Introduit en 2000 par un groupe d’acteurs technologiques majeurs, SATA a remplacé l’ATA parallèle et est rapidement devenu le protocole de système de stockage omniprésent pour les ordinateurs allant des ordinateurs portables aux serveurs. Au fil des ans, les révisions de la spécification ont été augmentées et elle fonctionne actuellement à 6 Gbit/s avec un débit effectif allant jusqu’à 600 Mbit/s.

Bien que développés pour la technologie des disques durs avec des plateaux de rotation mécaniques et des têtes de lecture / écriture commandées par un actionneur, les premiers disques SSD ont été commercialisés avec des interfaces SATA pour tirer parti de l’écosystème SATA existant. C’était une conception pratique qui a contribué à accélérer l’adoption du SSD, mais ce n’était pas – et n’est toujours pas – l’interface idéale pour les périphériques de stockage flash NAND et était de plus en plus considérée comme un goulot d’étranglement du système.

Conçu pour le flash, la vitesse et la faible latence de NVMe laissent SATA dans la poussière, et NVMe permet des capacités de stockage beaucoup plus élevées dans des facteurs de forme plus petits tels que M.2. Généralement, les paramètres de performance NVMe dépassent ceux de SATA de cinq fois ou plus.

SATA est peut-être plus établi avec un historique plus long et des coûts de mise en œuvre plus bas que NVMe, mais il s’agit clairement d’une technologie de disque dur qui a été modernisée sur des supports de stockage plus modernes.

SSD NVMe par rapport aux SSD SAS

NVMe prend en charge 64 000 commandes dans une file d’attente de messages unique et un maximum de 65 535 files d’E/S. En revanche, la profondeur de file d’attente d’un périphérique SAS prend généralement en charge jusqu’à 256 commandes et un lecteur SATA prend en charge jusqu’à 32 commandes dans une file d’attente.

Cependant, les SSD PCIe basés sur NVMe sont actuellement plus chers que les SSD SAS et SATA de capacité équivalente; bien que ce delta se réduise. En outre, les SSD NVMe d’entreprise haut de gamme peuvent consommer plus d’énergie que les SSD SAS ou SATA. L’Association professionnelle SCSI affirme que les SSD SAS plus matures offrent des avantages supplémentaires par rapport aux SSD PCIe NVMe, tels qu’une plus grande évolutivité, une pluggabilité à chaud et des capacités de basculement éprouvées. Les SSD PCIe NVMe peuvent également fournir un niveau de performance dont de nombreuses applications n’ont pas besoin.

Historique et évolution de NVM Express

Le groupe de travail NVMHCI (Non-Volatile Memory Host Controller Interface) a commencé à développer la spécification NVMe en 2009 et a publié la version 1.0 le 1er mars 2011. Le 1.0 les spécifications comprenaient l’interface de mise en file d’attente, le jeu de commandes NVM, le jeu de commandes d’administration et les fonctions de sécurité.

Le groupe de travail NVMHCI, communément appelé le groupe de travail NVM Express, a publié une mise à jour de la spécification NVMe le octobre. 11, 2012. NVMe 1.1 a ajouté la prise en charge des SSD avec plusieurs ports PCIe pour activer les E / S à trajets multiples et le partage d’espaces de noms. D’autres nouvelles fonctionnalités comprenaient des transitions d’état d’alimentation autonomes pendant les temps d’inactivité pour réduire les besoins en énergie et les réservations, permettant à deux hôtes ou plus de coordonner l’accès à un espace de noms partagé pour améliorer la tolérance aux pannes.

Le groupe de travail NVM Express a organisé son premier Plugfest en mai 2013 pour permettre aux entreprises de tester la conformité de ses produits à la spécification NVMe et de vérifier l’interopérabilité avec d’autres produits NVMe.

Le groupe de travail NVM Express a été incorporé sous le nom d’organisation NVM Express en mars 2014. Les membres fondateurs à l’époque comprenaient Cisco Systems, Dell, EMC, la filiale HGST de Western Digital, Intel, LSI, Micron Technology, NetApp, Oracle, PMC-Sierra, Samsung Electronics, SanDisk et Seagate Technology.

L’organisation NVM Express est plus tard connue sous le nom de NVM Express Inc. L’organisation à but non lucratif compte plus de 100 entreprises technologiques en tant que membres.

La spécification NVMe 1.2 est apparue en novembre. 3, 2014, avec des améliorations telles que la prise en charge des mises à jour du micrologiciel en direct, une gestion améliorée de l’alimentation et l’option de protection des données de bout en bout.

Le nov. Le 17 novembre 2015, l’organisation NVM Express a ratifié la version 1.0 de l’interface de gestion NVM Express (NVMe-MI) pour fournir une architecture et un ensemble de commandes permettant de gérer un sous-système de mémoire non volatile hors bande. NVMe-MI permet à un contrôleur de gestion d’effectuer des tâches telles que la découverte de périphériques SSD et de capacités, la surveillance de l’état et de la température et les mises à jour du micrologiciel non perturbées. Sans NVMe-MI, les responsables informatiques s’appuyaient généralement sur des interfaces de gestion propriétaires spécifiques au fournisseur pour permettre l’administration des SSD PCIe.

Améliorations des fonctionnalités de NVMe 1.3

NVM Express a publié NVMe 1.3 en juin 2017. Les points forts sont centrés sur sanitize operations, un nouveau cadre appelé Directives et améliorations de la virtualisation.

Lors d’une opération d’assainissement, toutes les données utilisateur du sous-système NVMe sont modifiées de sorte que la récupération n’est pas possible » à partir d’un cache, d’un support non volatile ou d’un tampon de mémoire de contrôleur « , selon une feuille de référence NVM Express. Les opérations d’assainissement sont recommandées lorsqu’un SSD est retiré ou réutilisé pour un nouveau cas d’utilisation. Les modes d’assainissement incluent l’effacement de bloc de bas niveau sur les médias NAND, le crypto-effacement pour changer une clé de cryptage de média et l’écrasement.

Le cadre de directives définit un mécanisme d’échange de données entre un hôte et un sous-système NVMe. Cela active le balisage des commandes par E/S et donne aux administrateurs informatiques la possibilité de configurer des attributs et des paramètres à signaler.

La première utilisation des directives est une fonctionnalité appelée Flux pour optimiser le placement des données afin d’augmenter l’endurance et les performances des SSD NAND. Traditionnellement, avant que de nouvelles données puissent être écrites sur le SSD, de gros blocs de données doivent d’abord être effacés.

La fonction Flux permet à un hôte d’utiliser un » identifiant de flux » pour indiquer les blocs logiques de stockage spécifiques appartenant à un groupe de données associées. Cela permet de baliser une lecture ou une écriture avec des données associées stockées dans d’autres emplacements.

Les améliorations apportées à la virtualisation définissent comment NVMe flash peut être utilisé dans un environnement de stockage partagé où des contrôleurs physiques et virtuels sont présents, y compris des contrôleurs de stockage primaires et des contrôleurs de stockage secondaires. NVM Express a déclaré que l’objectif était de permettre aux équipes de développement de consacrer un SSD spécifique à une machine virtuelle spécifique (VM).

Améliorations des fonctionnalités de NVMe 1.4

NVMe 1.4 a été introduit en juillet 2019. Cette dernière version inclut un certain nombre d’améliorations et de nouvelles fonctionnalités, notamment :

- L’aide à la reconstruction améliore la récupération des données et améliore les opérations de migration des données.

- Le journal des événements persistants conserve un historique de lecteur détaillé qui peut être utilisé pour le débogage et la détermination des causes des problèmes.

- Les ensembles NVM et le déterminisme des E/S améliorent les performances et la qualité de service (QoS).

- L’accès asymétrique à l’espace de noms (ANA) améliore les chemins multiples pour une haute disponibilité.

- Le tampon mémoire hôte (HMB) réduit la latence et facilite la conception du SSD.

- La région de mémoire persistante (PMR) permet aux systèmes hôtes de lire et d’écrire directement sur la mémoire vive dynamique (DRAM) que les SSD incluent avec leur flash principal, qui avait été utilisé principalement pour la mise en cache

Les nouvelles fonctionnalités nécessiteront que les fabricants de lecteurs flash mettent à niveau leurs produits pour intégrer les améliorations. De nouveaux pilotes seront également nécessaires pour les systèmes d’exploitation.

Facteurs de forme et normes NVMe

La nécessité d’une interface et d’un protocole de stockage pour mieux exploiter le potentiel de performance de NAND flash dans les environnements d’entreprise a été la principale impulsion derrière le développement de la spécification NVMe. Mais la réinvention de la norme de connexion a ouvert la porte à plusieurs types d’implémentations d’interface qui pourraient rester dans les limites de la nouvelle spécification tout en offrant une variété d’options d’implémentation.

En peu de temps, un certain nombre de facteurs de forme flash conformes aux spécifications NVMe sont apparus, notamment des cartes d’extension de type conventionnel (AIC) pour le bus PCIe et de nouveaux facteurs de forme pour les SSD baptisés M.2 et U.2.

- AIC. Le facteur de forme AIC permet aux fabricants de créer leurs propres cartes qui s’insèrent dans le bus PCIe sans se soucier des conceptions de baies de stockage ou des limitations similaires. Les cartes sont souvent conçues pour des cas d’utilisation spéciaux et peuvent inclure des processeurs supplémentaires et d’autres puces pour améliorer les performances du stockage à semi-conducteurs.

- M.2. Le M.le facteur de forme 2 a été développé pour tirer parti de la taille compacte du flash NAND et de la faible décharge de chaleur. En tant que tels, les appareils M.2 ne sont pas destinés à s’insérer dans les compartiments traditionnels de la baie d’entraînement, mais plutôt à être déployés dans des espaces beaucoup plus petits. Souvent décrits comme de la taille d’un bâton de gomme, les SSD M.2 mesurent 22 mm de large et généralement 80 mm de long, bien que certains produits puissent être plus longs ou plus courts.

- U.2. Contrairement au facteur de forme M.2, les SSD U.2 ont été conçus pour s’adapter aux baies de stockage existantes initialement destinées aux périphériques SATA ou SAS standard. U.2 SSD ressemblent beaucoup à ces anciens supports, car ils utilisent généralement les boîtiers de 2,5 pouces ou 3,5 pouces qui sont des boîtiers familiers pour les disques durs. L’idée, bien sûr, était de rendre aussi facile que possible la mise en œuvre de la technologie NVMe avec le moins de réingénierie possible.

Un autre facteur de forme NVMe moins largement déployé est le facteur de forme SSD d’entreprise et de centre de données, ou EDSFF. Il est soutenu par des acteurs clés de l’industrie du stockage, tels qu’Intel, Dell EMC, Hewlett Packard Enterprise (HPE), Lenovo, Samsung et d’autres. L’objectif de l’EDSFF est d’apporter des performances et des capacités supérieures aux systèmes de stockage de classe entreprise. L’exemple le plus connu de flash EDSFF est peut-être le E1 d’Intel.L (long) et E1.Dispositifs flash S (courts), qui sont fournis dans ce qu’on appelait à l’origine le facteur de forme « règle ».

NVMe sur tissus

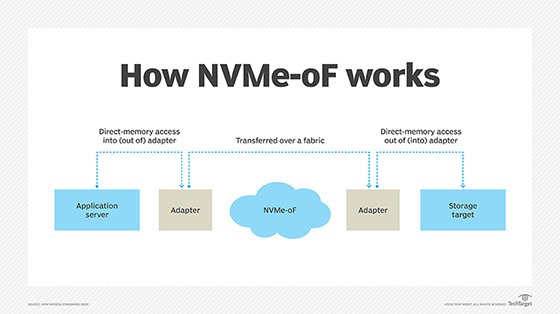

NVM Express Inc. publication de la version 1.0 de la spécification NVMe over Fabrics (NVMe-oF) le 5 juin 2016. NVMe-oF est conçu pour étendre les avantages haute performance et faible latence de NVMe sur les tissus réseau qui connectent les serveurs et les systèmes de stockage, tels que Fibre Channel (FC), Ethernet et InfiniBand.

Les transports de matrice incluent NVM-oF utilisant l’accès direct à la mémoire à distance (RDMA) et NVMe-oF mappé à FC. Un sous-groupe technique de NVM Express Inc. a travaillé sur NVMe-oF avec RDMA, et le comité T11 du Comité International des Normes de technologie de l’Information (INCITS) est responsable du développement de NVMe sur FC (FC-NVMe).

La spécification NVMe-oF est en grande partie la même que la spécification NVMe. L’une des principales différences entre NVMe-oF et NVMe est la méthodologie de transmission et de réception des commandes et des réponses. NVMe est conçu pour une utilisation locale et mappe les commandes et les réponses à la mémoire partagée d’un ordinateur via PCIe. En revanche, NVMe over Fabrics utilise un système basé sur des messages pour communiquer entre l’ordinateur hôte et le périphérique de stockage cible.

L’objectif de conception déclaré pour NVMe-oF était de ne pas ajouter plus de 10 microsecondes de latence pour la communication entre un ordinateur hôte NVMe et un périphérique de stockage NVMe connecté au réseau, par rapport à la latence associée à un périphérique de stockage NVMe utilisant le bus PCIe d’un ordinateur local.